- 您现在的位置:买卖IC网 > Sheet目录250 > SEN02G64C4BF2SA-30WR (Swissbit NA Inc)DRAM DDR2 2GB 200-SODIMM

�� �

�

�

�Data� Sheet�

�Rev.1.3�

�09.11.2010�

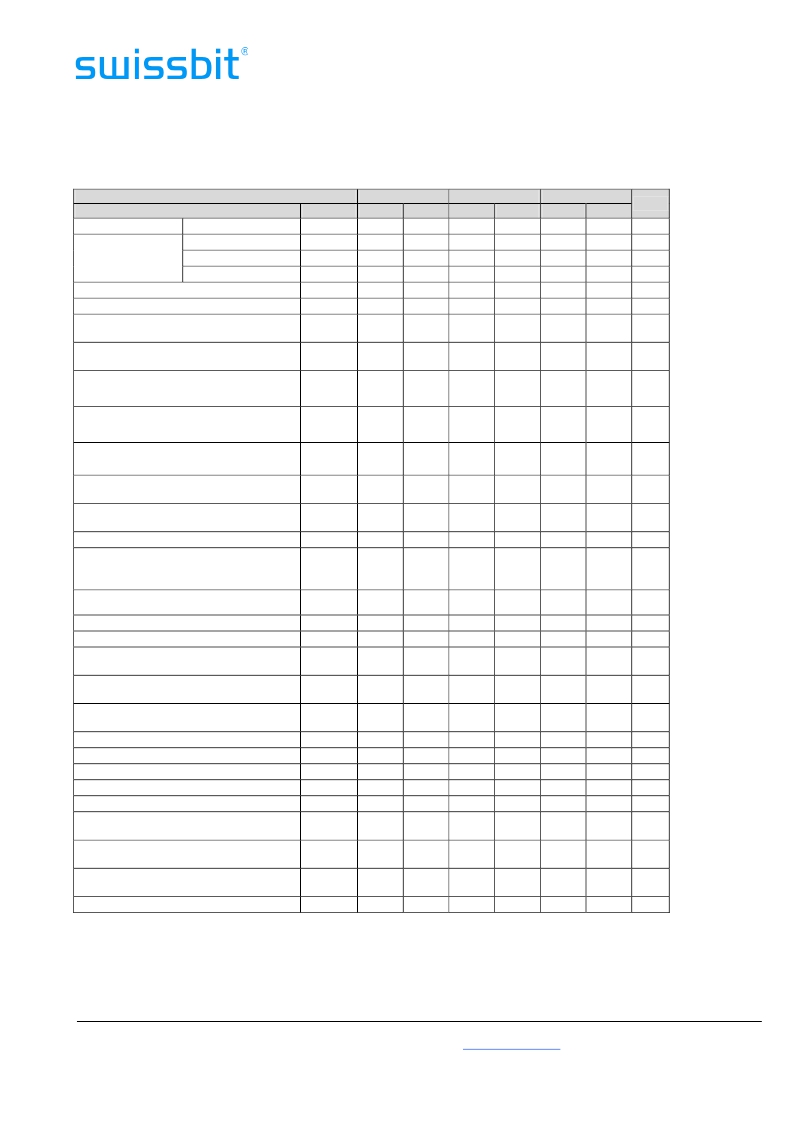

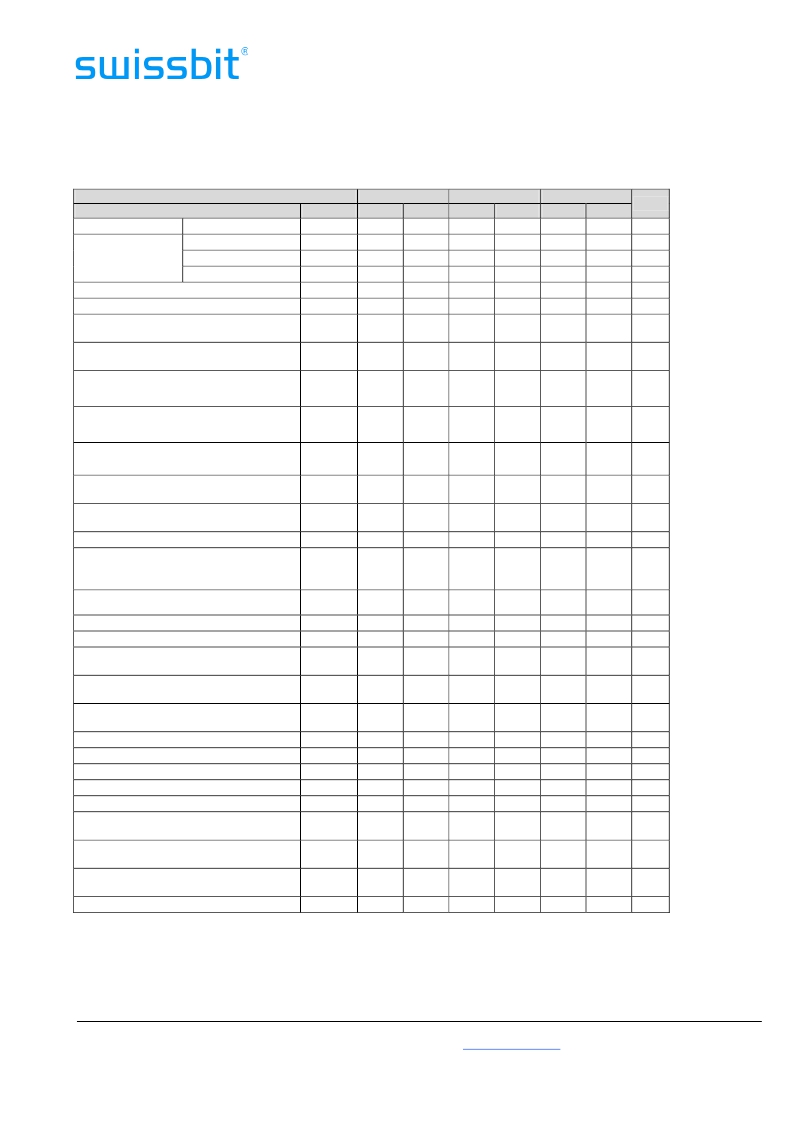

�DDR2� SDRAM� COMPONENT� ELECTRICAL� CHARACTERISTICS� AND� RECOMMENDED�

�AC� OPERATING� CONDITIONS�

�(0°C� ≤� T� CASE� ≤� +� 85°C;� V� DDQ� =� +1.8V� ±� 0.1V,� V� DD� =� +1.8V� ±� 0.1V)�

�AC� CHARACTERISTICS�

�PARAMETER�

�SYMBOL�

�6400-666�

�MIN� MAX�

�5300-555�

�MIN� MAX�

�4200-444�

�MIN� MAX�

�Unit�

�Clock� cycle� time�

�CL� =� 6�

�t� CK� (6)�

�2.5�

�8.0�

�-�

�+�

�-�

�-�

�ns�

�CK� high-level� width�

�CK� low-level� width�

�CL� =� 5�

�CL� =� 4�

�CL� =� 3�

�t� CK� (5)�

�t� CK� (4)�

�t� CK� (3)�

�t� CH�

�t� CL�

�3.0-�

�3.75�

�-�

�0.48�

�0.48�

�8.0-�

�8.0�

�-�

�0.52�

�0.52�

�3.0�

�3.75�

�5.0�

�0.45�

�0.45�

�8.0�

�8.0�

�8.0�

�0.55�

�0.55�

�-�

�3.75�

�5.0�

�0.45�

�0.45�

�-�

�8.0�

�8.0�

�0.55�

�0.55�

�ns�

�ns�

�ns�

�t� CK�

�t� CK�

�Half� clock� period�

�t� HP�

�min�

�min�

�min�

�ps�

�(t� CH,� t� CL� )�

�(t� CH,� t� CL� )�

�(t� CH,� t� CL� )�

�Access� window� (output)� of� DQ� S� from�

�CK/CK#�

�t� AC�

�-0.40�

�+0.40�

�-0.45�

�+0.45�

�-0.50�

�+0.50�

�ns�

�Data-out� high-impedance� window� from�

�CK/CK#�

�t� HZ�

�t� AC� max�

�+0.45�

�(=� t� AC�

�max)�

�+0.50�

�(=� t� AC�

�max)�

�ns�

�Data-out� low-impedance� window� from�

�CK/CK#�

�t� LZ�

�t� AC� min� t� AC� max�

�-0.45�

�(=� t� AC� min)�

�+0.45�

�(=� t� AC�

�max)�

�-0.50�

�(=� t� AC� min)�

�+0.50�

�(=� t� AC�

�max)�

�ns�

�DQ� and� DM� input� setup� time� relative� to�

�DQS�

�DQ� and� DM� input� hold� time� relative� to�

�DQS�

�DQ� and� DM� input� pulse� width�

�(for� each� input)�

�Data� hold� skew� factor�

�DQ-DQS� hold,� DQS� to� first� DQ� to� go� non-�

�valid,� per� access�

�Data� valid� output� window�

�DQS� input� high� pulse� width�

�DQS� input� low� pulse� width�

�DQS� falling� edge� to� CK� rising�

�-� setup� time�

�DQS� falling� edge� from� CK� rising� -� hold�

�time�

�DQS� –� DQ� skew,� DQS� to� last� DQ� valid,�

�per� group,� per� access�

�t� DS�

�t� DH�

�t� DIPW�

�t� QHS�

�t� QH�

�t� DVW�

�t� DQSH�

�t� DQSL�

�t� DSS�

�t� DSH�

�t� DQSQ�

�0.05�

�0.125�

�0.35�

�t� HP� -�

�t� QHS�

�t� QH� -�

�t� DQSQ�

�0.35�

�0.35�

�0.2�

�0.2�

�0.3�

�0.2�

�0.10�

�0.30�

�0.35�

�t� HP� -�

�t� QHS�

�t� QH� -�

�t� DQSQ�

�0.35�

�0.35�

�0.2�

�0.2�

�0.34�

�0.24�

�0.10�

�0.35�

�0.35�

�t� HP� -�

�t� QHS�

�t� QH� -�

�t� DQSQ�

�0.35�

�0.35�

�0.2�

�0.2�

�0.4�

�0.30�

�ns�

�ns�

�t� CK�

�ns�

�ns�

�ns�

�t� CK�

�t� CK�

�t� CK�

�t� CK�

�ns�

�DQS� read� preamble�

�DQS� read� postamble�

�t� RPRE�

�t� RPST�

�0.9�

�0.4�

�1.1�

�0.6�

�0.9�

�0.4�

�1.1�

�0.6�

�0.9�

�0.4�

�1.1�

�0.6�

�t� CK�

�t� CK�

�DQS� write� preamble�

�DQS� write� preamble� setup� time�

�t� WPRE�

�t� WPRES�

�0.35�

�0�

�0.35�

�0�

�0.25�

�0�

�t� CK�

�ns�

�DQS� write� postamble�

�Positive� DQS� latching� edge� to� associated�

�clock� edge�

�Write� command� to� first� DQS� latching�

�transition�

�t� WPST�

�t� DQSS�

�0.4�

�-� 0.25�

�WL-�

�t� DQSS�

�0.6�

�+� 0.25�

�WL+�

�t� DQSS�

�0.4�

�-� 0.25�

�WL-�

�t� DQSS�

�0.6�

�+� 0.25�

�WL+�

�t� DQSS�

�0.4�

�-� 0.25�

�WL-�

�t� DQSS�

�0.6�

�+� 0.25�

�WL+�

�t� DQSS�

�t� CK�

�t� CK�

�t� CK�

�Address� and� control� input� pulse� width�

�(for� each� input)�

�Address� and� control� input� setup� time�

�t� IPW�

�t� ISa�

�0.6�

�0.175�

�0.6�

�0.4�

�0.6�

�0.5�

�t� CK�

�ns�

�Swissbit� AG�

�Industriestrasse� 4�

�CH-9552� Bronschhofen�

�Fon:� +41� (0)� 71� 913� 03� 03�

�Fax:� +41� (0)� 71� 913� 03� 15�

�www.swissbit.com�

�eMail:� info@swissbit.com�

�Page� 9�

�of� 14�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

SER2LGYRDGNAUEE

SWITCH PUSH SPDT 0.01A 24V

SESD0201C-006-058

ESD PROTECTOR 0201 5.8V SILICON

SESD0201C-120-058

ESD PROTECTOR 0201 5.8V SILICON

SESD0201P1BN-0400-090

TVS DIODE 6V 1CH BI 0201

SESD0402Q2UG-0020-090

TVS DIODE 5V 2CH UNI SMD

SESD0402S-005-054

ESD PROTECT SOD-923 5.4V SILICON

SESD0402X1BN-0010-098

TVS DIODE 5V 1CH BI SMD

SESD0402X1UN-0020-090

TVS DIODE 5V 1CH UNI SMD

相关代理商/技术参数

SEN02G64C4BH2MT-25WR

制造商:SWISSBIT NA INC 功能描述:DDR2 2GB SODIMM 制造商:Swissbit 功能描述:DIMM / SO-DIMM / SIMM 2GB DDR2 SDRAM 64 bit SO-DIMM CL6

SEN-0541

制造商:SENSITRON 制造商全称:Sensitron 功能描述:POWER OPERATIONAL AMPLIFIER

SEN06464H2CH1MT-25R

制造商:SWISSBIT NA INC 功能描述:DDR2 512MB SODIMM

SEN06464H2CH1MT-25WR

制造商:SWISSBIT NA INC 功能描述:DDR2 512MB SODIMM 制造商:Swissbit 功能描述:DIMM / SO-DIMM / SIMM 512MB DDR2 SDRAM 64 bit SO-DIMM CL6

SEN06464H2CH1MT-30R

制造商:SWISSBIT NA INC 功能描述:DDR2 512MB SODIMM

SEN-08501

功能描述:ULTRASONIC RANGE FINDER - LV-MAX 制造商:sparkfun electronics 系列:LV-MaxSonar?-EZ? 包装:散装 零件状态:有效 频率:- 电压 - 额定:5V 光束孔径角:- 工作温度:- 标准包装:1

SEN-08502

功能描述:ULTRASONIC RANGE FINDER - LV-MAX 制造商:sparkfun electronics 系列:LV-MaxSonar?-EZ? 包装:散装 零件状态:有效 频率:42kHz 电压 - 额定:2.5 V ~ 5.5 V 光束孔径角:- 工作温度:- 标准包装:1

SEN-08503

功能描述:ULTRASONIC RANGE FINDER - LV-MAX 制造商:sparkfun electronics 系列:LV-MaxSonar?-EZ? 包装:散装 零件状态:有效 频率:42kHz 电压 - 额定:2.5 V ~ 5.5 V 光束孔径角:- 工作温度:- 标准包装:1